Percobaan 2 :

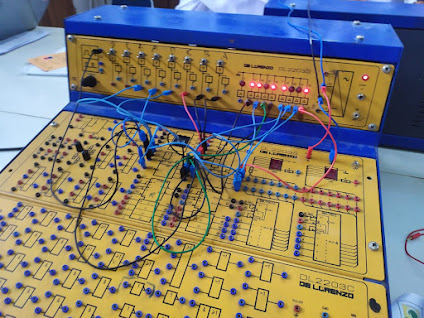

Module D'Lorenzo :

1. Saklar SPDT

SPDT (Single Pole Double Throw), merupakan golongan saklar yang memiliki 3 terminal. Jenis saklar ini dapat digunakan sebagai saklar pemilih. Contohnya, saklar pemilih tegangan input adaptor yaitu 110V atau 220V.

Spesifikasi :

Wideband (DC to 1 GHz)

Low through loss (1 dB typical at 200 MHz)

Unused input is terminated internally in 50

Excellent overload capability (1 dB gain compression point +18 dBm at 300 MHz)

Low DC power (170 A from 5 V supply)

Fast switching (20 ns typical)

Good isolation (off channel isolation 60 dB at 100 MHz)

Low distortion (IP3 intercept +33 dBm)

Good 50 match (return loss 18 dB at 400 MHz)

Full ESD protection

Bidirectional operation

Low through loss (1 dB typical at 200 MHz)

Unused input is terminated internally in 50

Excellent overload capability (1 dB gain compression point +18 dBm at 300 MHz)

Low DC power (170 A from 5 V supply)

Fast switching (20 ns typical)

Good isolation (off channel isolation 60 dB at 100 MHz)

Low distortion (IP3 intercept +33 dBm)

Good 50 match (return loss 18 dB at 400 MHz)

Full ESD protection

Bidirectional operation

2. IC 74l90

Berdasarkan percobaan 2a dengan menggunakan IC 74LS90 dan ic 7493 , sesuai jurnal jurnal kita memvariasikannya dengan variasi berikut

- Apabila B0=1, B1=1, B2=0, B3=don't care, B4=1, B5=1, maka output yang dihasilkan 0000 yang ditandai logicprobenya tidak menyala (off). Hal ini disebabkan karena pada counter IC 74LS90 sedang mereset sehingga ouput yang terbaca yakni 0000. selain itu hal ini terjadi karena pada logika B1 dan B0 nya sama-sama lohika satu yang artinya saat masuk ic karena ada NAND maka outputnya nol. sama juga halnya dengan input dari B4 dan B5 yang sama-sama berlogika 1.

- Apabila B0=1, B1=1, B2=don't care, B3=0, B4=0, B5=1, maka ouput yang terbaca pada counter IC 74LS90 yakni 0000 yang ditandai logicprobenya tidak menyala (off) karena sedang mereset kembali ke 0000. Sedangkan pada IC 7493, ouput yang dihasilkan ialah counter akan mencacah secara asyncronous dalam keadaan counter up dengan pola 1 dan 3hal ini terjadi karena pada input B4 dan B5 memiliki input 0 dan 1 sehingga saat masuk ic 7493 maka akan ada gerbang logika NAND sehingga outputnya 1 dan didapat counter up dengan pola 1 dan 3.

- Apabila B0=0, B1=0, B2=0, B3=1 B4=1, B5=0, maka ouput akan melakukan counter up 0-15 asyncronous baik counter IC 74LS90 maupun counter IC 7493 dengan 0-9.

- Apabila B0=0, B1=don't care, B2=0, B3=don't care, B4=0, B5=0, maka ouput akan melakukan counter up 0-15 asyncronous baik counter IC 74LS90 maupun counter IC 7493 dengan 0-9.

- Apabila B0=0, B1=don't care, B2=don't care, B3=0, B4=tidak dihubungkan, B5=tidak dihubungkan, maka ouput akan melakukan counter up asyncronous untuk counter IC 74LS90, sedangkan IC 7493 tidak aktif karena tidak dihubungkan yang ditandai logicprobenya tidak menyala (off).

- Apabila B0=don't care, B1=0, B2=don't care, B3=0, B4=tidak dihubungkan, B5=tidak dihubungkan, maka ouput akan melakukan counter up asyncronous untuk counter IC 74LS90, sedangkan IC 7493 tidak aktif karena tidak dihubungkan yang ditandai logicprobenya tidak menyala (off).

- Apabila B0=0, B1=don't care, B2=don't care, B3=0, B4=tidak dihubungkan, B5=tidak dihubungkan, maka ouput akan melakukan counter up asyncronous untuk counter IC 74LS90, sedangkan IC 7493 tidak aktif karena tidak dihubungkan yang ditandai logicprobenya tidak menyala (off).

- Apabila B0=don't care, B1=0, B2=0, B3=don't care, B4=tidak dihubungkan, B5=tidak dihubungkan, maka ouput akan melakukan counter up asyncronous untuk counter IC 74LS90, sedangkan IC 7493 tidak aktif karena tidak dihubungkan yang ditandai logicprobenya tidak menyala (off).

1. Analisa output Percobaan berdasarkan ic yang digunakan!

Jawab:

- Pada percobaan 2 ic yang digunakan ada dua yaitu IC 74lS90 dan 7493. Berdasarkan percobaan yang telah dilakukan, dapat disimpul kan bahwa IC 7IC 74lS90 merupakan counter yang dapat menghitung secara desinal dengan asycronos counter dari 0-9 (0000, 0001, 0010, 0011, 0100, 01, 01, 0110, 0111, 1000, 1001). kemudian dia akan reset ketika Bo dan BI berlogika 1, hal ini dapat kita lihat pada percobaan dijurnal pada percobaan 1 dan 2 yang output nya off. sedangkan kondisi lainnya IC 74490 akan tetap melakukan perhitungan dalam kondisi counter up asycronus

- Pada IC 7493 juga merupakan counter yang terhubung dengan B4 dan B5. IC 7493 dapat menghitung dari 0-19 (f) dimana dari binner 0000-1111. Berdasarkan Percobaan yang dilakukan, pada gurnal dapat kita lihat disaat B5 dan B4 sama berlogika 1 maka outputnya 0000 atau logicprobe nya mati jadi diadalam Ic tersebut terdapat Nand yang membalikan inputnya. maka jika Ingin dapat mengcounter maka salah satu Inpunya harus ada 0.

2. Analisa hasil kondisi 3 pada percobaan 2a dengan kondisi 3 pada percobaan 2b!

Jawab:

Hasil kondisi 3 pada percobaan 2a yaitu counter asychronus dengan pola yang acak, hal ini terjadi karena pada rangkain ke dua a ini CKA dan ckbnya terhubung ke clock. sedangkan percobaan 2 kondisi 3 pada 2b thenghasilkan Output yang berurutan hal ini terjadi kama ckbnya telah terhubung ke Qo, hal ini terjadi karena sesuai dengan prinsip dimana inputan dari flipfllop selanjutnya menunggu output dari Flipfllop sebelumnya. berdasarkan Perbandingan percobaan 2a dan 2b kondisi s diperoleh bahwa percobaan 2a diperoleh output biner 4 bit yang tidak teratur karena pengaruh 2 input clock yang digabung sedangkan percobaan 2b diperoleh output yang teratur karena rangkain input. CKA dan Ckb memenuhi sistem Asychronus yang dimana Input CKB diperoleh dari output dan pertama / sebelumnya sehingga terjadi input clock bergiliran.

3. Apa pengaruh clock A dan clock B pada ic yang digunakan?

Jawab:

Pengaruh dari clock A dan clock b yang digunakan adalah Sebagai Pengatur output pada Ic. dari input clock Ic yang digunakan yang merupakan aktif low sehingga saat clock dalam kondisi fall time, output Q dapat diperoleh dari keluaran Ic counter dan dapat berubah saat kondisi clock time. Pada CK A output yang dipengaruhinya adalan Qo dan Qa Sedangkan CKB yang dipengaruhinya adalah output QI dan qB. Prinsip kera Asycronus, input CKA diperoleh dan clock dan ckB diperoleh dan umpan feedback dari Output Qo dan QA Sehingga hasil perhitungganya dapat berurut. namun saat IC Counter Asychronos 741990 dan 1493 ini, pada Input CKA dan CKB dihubung serempak dengan clock sehingga Sistem kerja counter asychronous tidak teratur.

Link Datasheet 74LS90 Download

Link Datasheet 7493 Download

.jpeg)

Tidak ada komentar:

Posting Komentar