Percobaan 1 :

Module D'Lorenzo :

1. Saklar SPDT

SPDT (Single Pole Double Throw), merupakan golongan saklar yang memiliki 3 terminal. Jenis saklar ini dapat digunakan sebagai saklar pemilih. Contohnya, saklar pemilih tegangan input adaptor yaitu 110V atau 220V.

Spesifikasi :

Wideband (DC to 1 GHz)

Low through loss (1 dB typical at 200 MHz)

Unused input is terminated internally in 50

Excellent overload capability (1 dB gain compression point +18 dBm at 300 MHz)

Low DC power (170 A from 5 V supply)

Fast switching (20 ns typical)

Good isolation (off channel isolation 60 dB at 100 MHz)

Low distortion (IP3 intercept +33 dBm)

Good 50 match (return loss 18 dB at 400 MHz)

Full ESD protection

Bidirectional operation

Low through loss (1 dB typical at 200 MHz)

Unused input is terminated internally in 50

Excellent overload capability (1 dB gain compression point +18 dBm at 300 MHz)

Low DC power (170 A from 5 V supply)

Fast switching (20 ns typical)

Good isolation (off channel isolation 60 dB at 100 MHz)

Low distortion (IP3 intercept +33 dBm)

Good 50 match (return loss 18 dB at 400 MHz)

Full ESD protection

Bidirectional operation

2. JK Flip-Flop

JK flip-flop merupakan flip flop yang dibangun berdasarkan pengembangan dari RS flip-flop. JK flip-flop sering diaplikasikan sebagai komponen dasar suatu counter atau pencacah naik (up counter) ataupun pencacah turun (down counter). JK flip flop dalam penyebutanya di dunia digital sering di tulis dengan simbol JK -FF. Dalam artikel yang sedikit ini akan diuraikan cara membangun sebuah JK flip-flop menggunakan komponen utama berupa RS flip-flop.

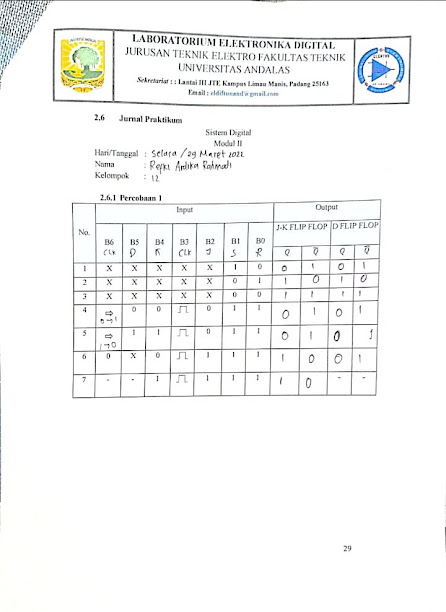

Tabel Kebenaran :

3. D Flip-Flop

Data flip-flop merupakan pengemangan dari RS flip-flop, pada D flip-flop kondisi output terlarang (tidak tentu) tidak lagi terjadi. Data flip-flop sering juga disebut dengan istilah D-FF sehingga lebih mudah dalampenyebutannya. Data flip-flop merupakan dasar dari rangkaian utama sebuah memori penyimpan data digital. Input atau masukan pada RS flip-flop adalah 2 buah yaitu R (reset) dan S (set), kedua input tersebut dimodifikasi sehingga pada Data flip-flop menjadi 1 buah input saja yaitu input atau masukan D (data) saja. Model modifikasi RS flip-flopmenjadi D flip-flop adalah dengan penambahan gerbang NOT (Inverter) dari input S ke input R pada RS flip-flop seperti telihat pada gambar dasar D flip-flop berikut.

Tabel Kebenaran :

Pertama tama kita ke JK flip flop, pada JK flipflop disini terlebih dahulu kita lihat berapa inputan pada kaki S dan R, jika pada salah satu inputan tersebut ada yang bernilai 1 maka ini merupakan rangkaian Asinkronous dimana untuk inputan J dan K diabaikan dan kita hanya berpatokan pada S dan R saja.

Selanjutnya dapat kita lihat pada rangkaian bahwa di dekat inputan kaki R dan S merupakan Aktif Low, maka jika inputan nya berlogika 1 atau aktif high maka inputnya mati atau berlogika 0, jadi pada kaki RS sama sama bernilai 1 maka R dan S dapat diabaikan. Selanjutnya baru kita lihat ke inputan J-K. Disini inputan J berlogika 0 dan K berlogika 1 pada inputan JK merupakan aktif High, berarti aktif pada logika 1, untuk Clock aktif low, maka sinyal akan berganti naik dan turunya pada keadaan fall time atau dari keaadaan 1 menuju 0.Selanjutnya untuk tabel kebenaran karena J=0, K=1 maka output akan berlogika 0 dan 1.

Kedua pada D Flip Flop, D flipflop sendiri inputan yang awalnya dua digabung menjadi 1 dimana pada kaki bawahnya diberi gerbang not sehingga selalu berkebalikan dengan inputan sebelum kita masuk ke inputan D maka kita harus melihat inputan SR, apakah salah satunya memiliki inputan. Disini inputannya tidak Ada dikarenakan sinyal awalnya berlogika 1, sedangkan rangkaianan tersebut aktif low. maka S dan R tidak aktif awalnya. Jadi di sini clocknya merupakan aktif high sehingga output akan berpindah ketika kondisi rise time yaitu ketika perpindahan 0 ke 1. Disini inputan D di kondisi adalah 1 maka inputan D aktif atau berlogika 1 sehingga pada tabel logika akan menghasilkan output 1 dan Q aksen 0,sesuai dengan tabel kebenaran.

1. Bagaimana jika B0 dan B1 sama sama diberi logika 0, apa yang terjadi pada rangkaian?

Jawab :

Apabila B0 dan B1 sama-sama bernilai 0, maka untuk output yang dihasilkan adalah Q=1 dan Q'=1. Kondisi ini disebut kondisi terlarang dimana keadaannya tidak stabil. Untuk nilai Q=1 dan Q'=1 ini didapatkan karena rangkaiannya bersifat aktif low dimana ia akan aktif saat diberi masukan 0. Oleh sebab itu, outputnya bernilai satu. Jadi kondisi ni disebut kondisi terlarang dimana kondisinya tidak stabil.

2. Bagaimana jika B3 diputuskan/tidak dibubungkan pada rangkaian apa yang terjadi pada rangkaian?

Jawab :

Apabila B3 diputuskan/tidak dihubungkan maka hal itu berpengaruh terhadap J-K Flip Flop. Ini disebabkan karena yang terhubung ke clock pada J-K Flip Flop adalah B3. Apabila input dari J dan K divariasikan, maka tidak akan mengalami perubahan pada outputnya, karena nilai untuk J-K Flip Flop dipengaruhi oleh clock. Tetapi, nilai J-K Flip Flop bergantung pada nilai set dan reset sesuai dengan sifat inputnya yaitu aktif low. Sehingga jika inputnya bernilai 0 maka outputnya bernilai 1, dan jika inputnya bernilai 1 maka outputnya bernilai 0. Dan untuk D Flip - Flop sendiri tidak berpengaruh, karena clocknya masih ada.

3. Jelaskan apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang pada Flip-Flop!

Jawab :

Kondisi toggle

Merupakan kondis yang terjadi saat input J dan K bernilai 1 dimana input J = 1 dan K = 1. Maka untuk outputnya berubah-ibah. Untuk nilai ouput yang berubah-ubah inilah yang disebut dengan toggle. Kondisi toggle juga disebut situasi dimana Flip - Flop memiliki keluaran yang berganti - ganti, contohnya jika outputnya Q = 1 dan Q' = 0, pada togglenya akan berlaku pergantian sehingga outputnya menjadi Q = 0 dan Q'=1. Jadi kondisinya adalah berubah.

Kondisi not change

Merupakan kondisi pada Flip - Flop dimana Flip - Flop akan mempertahankan kondisi sebelumnya atau tidak mengalami perubahan. Contohnya, jika output Q =1 dan Q'=0 maka Q'=0 tidak mengalami perubahan. Kondisi ini terjadi ketika inputnya sama - sama berlogika 0 dimana output yang dihailkan sama dengan output pada percobaan ssebelumnya.

Kondisi terlarang

Merupakan kondisiyang terjadi jika output yang dihasilkan sama sma 1 yaitu Q=1 dan Q'=1. Ini disebut terlarang karena nilai QVdan Q' seharusnya bernilai berlawanan. Kondisi ini sebaiknya dihindari karena dapat meruska alat saat disimulasikan maupun diaplikasikan.

Link Datasheet SN74LS73AN Download

.png)

Tidak ada komentar:

Posting Komentar